# Eliminating Timing Information Flows in a Mix-Trusted System-on-Chip

Jason Oberg and Ryan Kastner

University of California, San Diego

**Timothy Sherwood**

University of California, Santa Barbara

### Editor's notes:

Integration of untrusted third-party IPs into an SoC design is a major challenge in establishing trustworthiness of the entire SoC. This article presents an approach to ensure information flow isolation between trusted and untrusted IP cores

—Swarup Bhunia, Case Western Reserve University

■ COMPUTING SYSTEMS GOVERN some of the most critical aspects of our lives. These high-assurance systems, which are found in medical devices, automobiles, planes, satellites, and military systems, have an extremely high cost of failure. Incorrect construction or unnoticed security holes can completely compromise their reliability, potentially putting humans in harms way of both their safety and privacy.

These systems have already seen their fair-share of security issues. For example, cardiac pacemakers have been shown to have weak radio frequency (RF) security. This can be exploited to compromise both a patient's personal safety and their secrecy [1]. Aside from medical devices, security holes in automobiles have been exploited to show that many of the critical components (such as the braking sys-

Digital Object Identifier 10.1109/MDT.2013.2247457

Date of publication: 14 February 2013; date of current version: 29 May 2013.

tem) can be remotely controlled by an attacker [2]. As is apparent with these examples, taking the utmost care in security when designing these systems is mandatory. However, in order to do so, designers need methods and tools

that can help them expose security issues.

Some standards exist, such as the Common Criteria standard that specifies a set of rules in which secure systems must be constructed and evaluated. For example, the Evaluation Assurance Level (EAL) is awarded to systems based on how thoroughly they have been evaluated (assigned a number from 1 to 7). Not surprisingly, achieving a high-assurance level is not only time consuming, but extremely expensive. Furthermore, it is nearly impossible to evaluate a system with components from untrusted entities because their behavior must be essentially assumed to be undefined. Because it is substantially faster and more cost efficient to use third-party components, it is desirable to construct a system that shows isolation between trusted, in-house built components, and potentially untrusted third party ones.

System-on-chips (SoCs) find themselves at the heart of these issues because they rely on the reuse of third-party intellectual property (IP) cores. These cores include memories, digital signal processors

(DSP), graphical processing units (GPUs), analog RF blocks, I/O interfaces, and other various hardware accelerators (such as hardware encryption units). The SoC tightly integrates these cores together using an SoC bus architecture such as the Opencores WISHBONE. Ideally, integration of these components would be done in a realiable and secure manner. Unfortunately, because many of these cores come from potentially untrusted sources, their use in high-assurance applications becomes extremely limited. This stems from the fact that these cores either come from an untrusted vendor or they have not been evaluated to the same extent as the trused cores. For example, the Mars Rover requires separation between the flight critical and scientific measurement systems simply because the flight critical components require detailed evaluation far beyond that of the measurement ones. A missed bug or vulnerability in the measurement components could affect the flight control components and desecrate the integrity the entire system.

One concern in mix-trusted SoC integration is because of malicious inclusions such as hardware trojans. These trojans can violate security by using hidden circuitry to either covertly transmit information or insert a kill switch into the system. A survey by Tehranipoor et al. [3] covers many of the detection techniques including power and timing-based analyses. The work we present here can help deal with hardware trojans, but requires additional techniques to help mitigate their effect. We can ensure hardware trojans in untrusted cores do not affect trusted ones but we must explicitly assume trusted cores do not have trojans.

Secure mix-trusted integration is not impossible if appropriate techniques are in place to build the system securely from the ground up. By designing a secure computing foundation, information flow can be tightly bounded in the system. Such techniques are hard to come by because information can flow through difficult to detect side-channels<sup>1</sup> in hardware; e.g., the amount *time* a computation takes to execute. Recently, researchers have put effort in

<sup>1</sup>A side-channel is defined as an entity that leaks information but was not intended for communication. The two most common side channels found in hardware are from timing (the data-dependent latency of a computation) and power (the data-dependent power consumed during a computation). In this work, we address only logical side-channels (timing), physical ones (power) are out of the scope of this paper.

developing these strategies, specifically with the use of *information flow tracking* at the lowest digital abstraction: logic gates.

Gate-level information-flow tracking (GLIFT) [4] uses additional logic to monitor the security level of every bit in the system as they flow through Boolean gates. Similar to information-flow tracking at higher abstractions [5], [6], GLIFT associates a single-bit security label (known as taint) to each data-bit and tracks this information as it flows through the system. This meta-data specifies the security level of every bit in the system and the extra logic gates to precisely monitor this meta-data to determine where the original data is moving. Because GLIFT works at the lowest digital abstraction, it is also capable of tracking information through timing channels as recently demonstrated [7]. This strong property makes it possible for testers and designers to determine whether or not untrusted information is flowing to trusted components so they have a sense of the potential security flaws in their designs. In the past, GLIFT has been used to show how to build a provably secure processor [8] and show isolation in the I2C and USB bus protocols [9]. There has not, to the best of our knowledge, been work showing how GLIFT can be used to show isolation in a larger, realistic SoC that uses components from varying trust.

The goal of this paper is to show how a SoC can be designed using cores from different trust levels and have its security tested using GLIFT. In doing so, we demonstrate that untrusted cores never affect trusted ones. Specifically, we target the WISHBONE [10] SoC protocol using a crossbar interconnect. We design a realistic system that resembles what one might find in high-assurance applications; specifically, two processors (trusted and untrusted) that want to share a hardware accelerator (AES encryption unit) in the SoC. Ideally, this sort of behavior should be allowed as long as the untrusted component does not interfere with the trusted one (and thereby compromise the integrity of the system). Using GLIFT, we show how a crossbar can be designed and tested to be information flow secure such that the untrusted processor never affects the trusted one. This allows the hardware accelerator to be shared in a secure way without causing harmful side effects to the trusted computation. We demonstrate that this isolation is maintained across several different scenarios in which the untrusted processor is attempting to interfere with the trusted one.

56

# Gate-level information-flow tracking (GLIFT)

GLIFT is a tracking technique targeted at the movement of information through Boolean gates. It has been used in a variety of applications, e.g., demonstrating isolation between devices in bus protocols [9] and processes in a microprocessor [8].

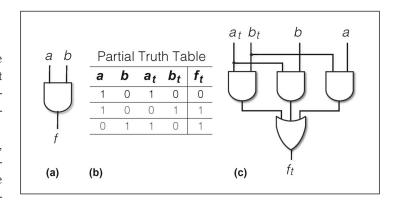

As with other information flow tracking methods, GLIFT associates a bit of meta-data (henceforth referred to as taint) and tracks this taint through the system as it executes. This bit of meta-data represents the security of the data (either trusted or untrusted) so that the flow of untrusted information can be precisely monitored. For example, consider a simple AND gate and partial truth table as shown in Figure 1.

Here we have a simple AND gate (a) with inputs aand b and also the tracking logic for this AND gate (c) with taint inputs  $a_t$  and  $b_t$  in addition to the original data inputs. The partial truth table (b) specifies how the GLIFT logic (c) tracks the taints of the inputs to the output. For example, as shown in row 1, if a is tainted ( $a_t = 1$  or a is untrusted) with a = 1 and b is not tainted with b = 0 then no tainted information (from a) flows through the logic gate because the output is always 0 because b = 0. In other words, a cannot affect the output f of the AND gate in this scenario. The tracking logic captures this property by indicating f as untainted ( $f_t = 0$ ). Conversely, if we consider row 2 in which b is tainted instead of a, then tainted information does flow through the AND gate because b affects the output f. This is captured by the GLIFT logic by labeling f as tainted ( $f_t = 1$ ). Similar truth tables can be constructed for other gate primitives (OR, XOR, etc.) so that GLIFT logic can be created for any gate in the design.

To use GLIFT in practice, the existing logic synthesis tools are leveraged to tightly integrate it into the design flow. First, we take a design written in a hardware-description language (HDL) such as Verilog or VHDL at the register-transfer level (RTL). This hardware design is then synthesized to logic gates using Synopsys' Design Compiler and target its and\_or.db library that contains simple two-input ANDs, ORs, and inverters. Note that we use this library for the sake of simplicity; more complex libraries can be used as long as the GLIFT logic has been derived *a priori* as previously discussed. Once the logic is in the form of a gate-level netlist, we process this netlist to add the additional GLIFT logic.

Figure 1. (a) A simple AND gate. (b) A partial truth table for the tracking logic of an AND gate.  $f_t = 1$  iff a tainted input affects  $f_t$ . (c) The tracking logic for an AND gate.

This process simply takes every gate primitive and replaces it with the appropriate GLIFT logic (this new logic contains both the original and tracking logic).

Once all the pieces are in place, the design can be tested to determine whether or not an information flow exists. This is done by tainting known untrusted regions of the design and simulating execution on input test vectors using a simulation tool such as Mentor Graphics Modelsim. If this tainted information flows to a trusted region, the design has a security vulnerability that the designer must assess. While GLIFT itself does not provide any mechanism for determining why there is a security-violating information flow, it will always correctly indicate the absence of one. We reserve providing the techniques for showing "why" for a future work. For now, it is up to the designer to reason about the flow and put mechanisms in place to eliminate it. GLIFT will, as mentioned, correctly identify the absence of this flow once these mechanisms are added. (Note that using GLIFT in this manner will show the absence of a flow for the test vectors used. It does not necessarily guarantee the absence of unintended information flow for all input combinations. Past work has created a solution to this problem called Star-Logic [8], but it is out of the scope of this paper.)

To show how this works more concretely, we show how to apply this technique to a realistic SoC with the WISHONE bus architecture. We undergo this test in a similar manner as has past work [9]. However, the system we present here is much more realistic and complex and provides a clearer sense as to how GLIFT can be applied to modern designs. The

March/April 2013 57

details of this system, and how we create an information-flow secure interconnect for WISHBONE, are presented in the next section.

# Designing a secure crossbar in WISHBONE

WISHBONE is a SoC protocol originally developed by the Opencores community. It is a relatively simple protocol that allows easy integration of different cores into a design. WISHBONE itself is very flexible and allows many different interconnect configurations and bus transactions. WISHBONE allows many connectivity configurations including:

point-to-point, data-flow, shared bus, and crossbar interconnect. In this paper, we focus on the crossbar interconnect because it provides a flexible interface for systems that contain large numbers of cores interacting in parallel.

We wish to demonstrate that multiple cores can access a shared resource in a safe and secure manner. We designed a system that consists of two MIPS-based processors and a 128-bit Advance Encryption Standard (AES) core. The two processors share the AES core over the WISHBONE interface. We assume that one of these processors runs critical code while the other is untrustworthy, e.g., running

unknown (potentially malicious) code or not being as thoroughly evaluated as the trusted core. Further details of this system are discussed in the next subsection.

# Mix-trusted system with hardware accelerator

Our system consists of two MIPS-based processors and a 128-bit AES core. We designed the MIPS based processor and the 128-bit AES was obtained from the Opencores [11] website. All cores are written in Verilog HDL. We chose this configuration because it well suits the common issues found in high-assurance applications. Namely, it is often desirable to share a hardware accelerator in a large SoC with mix-trusted components. Although this system is does not have all the complexity of commercial SoCs it does capture the main idea that multiple mix-trusted cores share common hardware resources and isolation between them should be maintained.

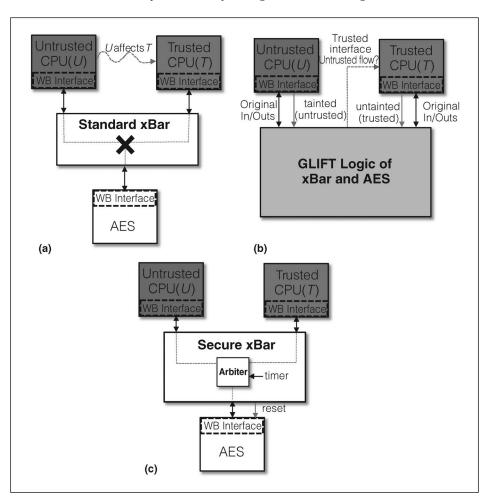

Figure 2a shows the overview of our system. It consists of two of our processors and a 128-bit hardware AES unit. One of these processors is treated as

Figure 2. (a) The system used in our test scenario. This consists of two MIPS-based processors and a 128-bit AES encryption core. U and T contend for the use of the AES core. (b) The system after the AES core, xBar, and interface controllers have their GLIFT logic added. Information is observed to flow from U to T. (c) The final information flow secure system uses a time-multiplexed arbiter with a trusted reset to ensure information flow isolation between U and T. Adding the GLIFT logic to this system shows no information flowing from U to T.

58 IEEE Design & Test

untrusted (U) and the other trusted (T). In other words, we do not trust the behavior of processor Uand assume its intentions are to corrupt the execution of T. Our MIPS-based processor is fully functional and can execute many of the SPEC 2006 benchmarks (e.g., mcf, specrand, bzip2) [12]. To execute these applications (that are written in C), we used the SESC gcc cross-compiler to compile to MIPS binaries. These binaries are loaded into our processor's memory and the executions are simulated using Mentor Graphics' Modelsim. In order to communicate off-chip, we memory-mapped our processors WISHBONE I/O controller to a region of unused memory space. Since we have a crosscompiler for our processor, we wrote C-applications to push data out of the WISHBONE I/O interface. We wrote different applications for U and T to execute as we discuss later.

We also designed the crossbar interconnect to handle requests from the processors. The crossbar interconnect is connected to each processor's WISHBONE controller (see Figure 2a). This crossbar interconnect handles requests from the two processors in a roundrobin fashion. This is simply for correctness and to prevent any sort of denial of service. Each processor can perform at most one transaction before having to relinquish control of the bus. It waits for requests from a master and grants access to the slave at the address specified if the slave is available. In our scenario, we have only a single slave: a 128-bit hardware AES unit. Depending on the request type, this AES unit will take the data passed to it (in 32-bit chunks) and encrypt/decrypt a 128-bit block. The processor that requested the bus cycle polls until the transaction is complete and then retrieves the data from the AES unit. Upon completion, the next processor (if it has a pending request) will get access to the AES core.

Note that all the communication between the processor and AES unit are through WISHBONE and its crossbar interconnect. In this system, because we have both trusted and untrusted processors contending for the use of the AES unit, there is likely to be information flows from U to T. Such a flow would violate the integrity of T and should be prevented. Moreover, this interference is not a denial of service attack because it is not possible for U to keep T from completing its work. Still, U can effect when T gets access to the AES block because it must wait for U's transaction to complete. For example, if U never

wants to use the bus, and T performs continuous bus transactions, T can finish in some time t. However, if U performs bus transactions every time it is scheduled, T will finish its bus transactions in time  $\approx 2t$ . Thus U can affect the time in which T finishes execution but cannot prevent it from doing so. The next section discusses how we identify information flows in this system and how to eliminate them.

# Building a secure crossbar for WISHBONE

To first illicit how an information flow occurs from U to T, we test a scenario in which T encrypts a 128-bit block of text using the AES unit and subsequently decrypts the cipher-text to verify the result. In parallel with T, U continuously reads a configuration register on the AES core. We call this program executing on processor U as  $R\_CONF$ . This scenario was chosen to show an information flow because U is not overwriting any of T's data because it is only reading. In other words, U is not directly corrupting T's data on the AES block and at first glance U seems to be noninterfering with T.

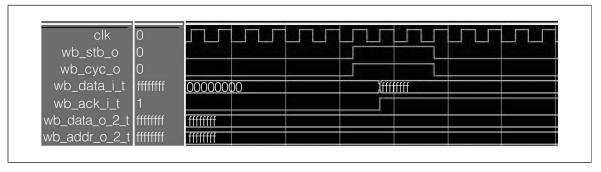

Since we are concerned with the information flow from U to T, we need to look at the information flowing out of U and in to T. To be precise, let  $T_{in_t} = \{data\_i_t, ack\_i_t\}$  be the taint input wires to T from the wishbone logic. We determine whether or not a flow occured by identifying whether any wire in  $T_{in_t}$  is every set to 1. To do so, we must track the flow of information through the crossbar, the AES unit's WISHBONE controller, and the AES unit itself. To track this flow of information, we follow the same method presented in Gate level information flow tracking. Namely, we process the crossbar and the AES unit with its WISHBONE interface through synthesis using Synopsys' Design Compiler to achieve a gate-level netlist. Subsequently, we add the GLIFT logic to these components and re-insert this logic into the system as shown in Figure 2b. We then execute  $R\_CONF$  on U by simulating the Verilog in Modelsim. From the simulation, as shown in Figure 3, a tainted flow is observed entering T's inputs as soon as it requests an AES transaction  $(\{data\_i_t, ack\_i_t\} = \{0xF...F, 1\})$ . Because we only tainted the ouputs of U, it must be the source of this tainted information flow.

This flow occurs because U and T contend for the use of the encryption unit. Specifically, U affects the execution of T indirectly by its use of the

March/April 2013 59

Figure 3. Waveform showing tainted information flow. As soon as T requests access to the AES unit  $(wb\_stb\_o = wb\_cyc\_o = 1)$  tainted information flows to its inputs  $(\{data\_i\_t, ack\_i\_t\} = \{0xF...F, 1\})$ . U's outputs were the only marked as tainted, so this flow must have originated from U.

AES unit. This flow can be regarded as occurring through a timing channel. That is, U is able to affect the *time* in which T finishes its computation (U is only reading and therefore does not directly affect the computation of T). Such channels can violate the integrity of the design because they can potentially violate real-time constraints, where Tmust meet a critical deadline but is unable to because of U. To solve this problem, we put in place a way for *U* to never affect *T*'s use of this resource. Specifically, we introduce a time-multiplexed arbiter with a *trusted reset* to the crossbar that forces *T* and U to operate in mutually exclusive time slots as shown in Figure 2c. Upon expiration of a time-slot, the logic is restored to a known state to ensure harmful content is left behind. As we see in the next section, this new crossbar eliminates this untrusted flow.

## Secure crossbar evaluation

To demonstrate the lack of information flow using this new crossbar, we construct several different programs that have malicious characteristics of causing interference to the trusted computation on T. Specifically, we show noninterference for a fixed set of programs. Noninterference states that U should never affect T through any sort of digital information. This includes both directly corrupting the data of T or affecting the time in which programs on T take to complete. This ensures not only the integrity of the data on T, but also the integrity of the timing of the computation. To demonstrate this property for a set of programs, let  $P = \{p_1, p_2, \ldots, p_n\}$  be a set of programs to be run on U. We want to show noninterference with respect to P by demonstrate

strating that no untrusted information flows to the inputs of T

$$\forall p \in P.S(p||\tau) \stackrel{c}{\Rightarrow} T_{in_t} = \{0, 0\}$$

(1)

where  $S(p||\tau)$  is the system executing with p on U and  $\tau$  on T and  $\stackrel{c}{\Rightarrow}$  is an implication over all clock cycles c.  $T_{in_t}$  is the set of taint inputs from the wishbone crossbar as previously defined. This definition says that for any program p in a set P, when executing p on U with some trusted computation on  $\tau$  on T, no untrusted information from U flows to the inputs of T during any clock cycle. Because GLIFT can also capture information flowing through timing channels as mentioned in the previous section, this includes information that affects the time in which  $\tau$  takes to complete.

For our particular test scenario, we build the set  $P = \{MM, R\_CONF, R\_ALL, W\_ALL, AES\}.$  MM is a simple matrix multiply program. R\_CONF is the same program as before that continuously reads a configuration register on the AES core. R\_ALL attempts to read the entire address space associated with the AES core. W\_ALL attempts to write the entire address space associated with the AES core. Last, AES uses the AES core to encrypt then decrypt some information. All of these applications are written in C, compiled to MIPS, and loaded on to their respective processor's instruction memory. Table 1 presents an interesting subset of our test cases and summarizes the outcomes. We do not present all results due to space constraints but observed that Definition 1 holds for each  $\tau$  we tested.

For all cases in which  $\tau$  accesses the WISHBONE fabric, untrusted information flows from U to T in

60 IEEE Design & Test

Table 1 Description and results of different applications executed on U and T. Untrusted flows are identified in the base cross bar for most scenarios and none are identified in the secure crossbar. Flows do not occur if T does not use the WISHBONE interface as in the cases of running MM.

| p on $U$ | au on $	au$ | Description                                                            | Flow in Secure<br>xBar | Flow in Base<br>xBar |

|----------|-------------|------------------------------------------------------------------------|------------------------|----------------------|

| AES      | MM          | U encrypts, decrypts, and validates result; T executes matrix-multiply | NO                     | NO                   |

| MM       | AES         | MM executes on U while T encrypts, decrypts, and validates result      | NO                     | YES                  |

| R_CONF   | AES         | Repeatedly read the status register on AES core                        | NO                     | YES                  |

| $R\_ALL$ | AES         | Read entire address space of AES core                                  | NO                     | YES                  |

| $W_ALL$  | AES         | Write entire address space of AES core                                 | NO                     | YES                  |

| AES      | AES         | Both encrypt, decrypt, and verify result                               | NO                     | YES                  |

the unsecure crossbar, thus violating Definition 1. One interesting case is when  $\mathit{MM}$  and  $\mathit{AES}$  are run on  $\mathit{T}$  and  $\mathit{U}$  respectively. In this case, no untrusted information flows to  $\mathit{T}$  simply because  $\mathit{\tau}$  never accesses the AES core. Its execution is independent of the behavior of  $\mathit{U}$ . Conversely, another interesting case arises when  $\mathit{U}$  runs  $\mathit{MM}$  and  $\mathit{T}$  runs  $\mathit{AES}$ . In this case, even though  $\mathit{p}$  is not using the AES core, the  $\mathit{lack}$  of its use still affects the behavior of  $\mathit{\tau}$ . This lack of use allows  $\mathit{\tau}$  to finish faster than if  $\mathit{p}$  were accessing it; a flow of information. GLIFT indicates no flow  $(\mathit{T}_{\mathit{in}_t} = \{0,0\})$  for all applications when the secure crossbar is used. In other words, non-interference is upheld for these computations on  $\mathit{U}$ .

It is important to make a couple of notes on this solution. First, the arbiter only time-multiplexes this specific resource and not the crossbar as a whole. The goal of the crossbar interconnect is to allow parallelism; multiplexing the entire crossbar eliminates this flexibility. This parallelism can still be maintained because U can be granted access to other devices in the system in parallel with T and isolation can still be maintained. In addition, ideally this property (Definition 1) would be shown for all possible programs on U to demonstrate complete noninterference. However, such an exhaustive test would be impractical in this case. Some recent work on GLIFT has made an effort to solve this problem by introducing Star-Logic [8] that uses an abstract execution to make exhaustive testing possible. Unfortunately most of this work is still in its early stages, but we plan to employ these techniques in future research.

**COMPUTERS ARE FINDING** themselves at the heart of avionics, medical devices, military applications, automobiles, and many other critical aspects of our lives. Building these systems in a secure

manner requires strict design practices and tools. In this paper, we showed how mix-trusted IP cores can be integrated in a secure manner. By using gate-level information flow tracking to show information flow isolation between trusted and untrusted cores, we have constructed a secure crossbar interconnect for the WISHBONE SoC bus architecture. This powerful property makes it possible to integrate mix-trusted cores and verify the security of their interactions. This ultimately reduces the cost and time associated with development and makes using untrusted cores in high-assurance applications more of a possibility.

# ■ References

- [1] D. Halperin, T. S. Heydt-Benjamin, B. Ransford, S. S. Clark, B. Defend, W. Morgan, K. Fu, T. Kohno, and W. H. Maisel, "Pacemakers and implantable cardiac defibrillators: Software radio attacks and zero-power defenses," in *Proc. IEEE Symp. Security* and *Privacy*, 2008, pp. 129–142.

- [2] K. Koscher, A. Czeskis, F. Roesner, S. Patel, T. Kohno, S. Checkoway, D. McCoy, B. Kantor, D. Anderson, H. Shacham, and S. Savage, "Experimental security analysis of a modern automobile," in *Proc. IEEE* Symp. Security and Privacy ("Oakland") 2010, 2010, pp. 447–462.

- [3] M. Tehranipoor and F. Koushanfar, "A survey of hardware trojan taxonomy and detection," *IEEE Des. Test Comput.*, vol. 27, no. 1, pp. 10–25, 2010.

- [4] M. Tiwari, H. Wassen, B. Mazloom, S. Mysore, F. Chong, and T. Sherwood, "Complete information flow tracking from the gates up," in *Proc. ASPLOS* 2009, 2009.

- [5] G. E. Suh, J. W. Lee, D. Zhang, and S. Devadas, "Secure program execution via dynamic information flow tracking," in *Proc. ASPLOS 2004*, 2004, pp. 85–96.

March/April 2013

- [6] J. R. Crandall and F. T. Chong, "Minos: Control data attack prevention orthogonal to memory model," in *Proc. MICRO* 2004, 2004, pp. 221–232.

- [7] J. Oberg, S. Meiklejohn, T. Sherwood, and R. Kastner, "A practical testing framework for isolating hardware timing channels," in *Proc. Design Automat. Test Eur.* (DATE), 2013.

- [8] M. Tiwari, J. Oberg, X. Li, J. Valamehr, T. E. Levin, B. Hardekopf, R. Kastner, F. T. Chong, and T. Sherwood, "Crafting a usable microkernel, processor, and I/O system with strict and provable information flow security," in *Proc. ISCA 2011*, 2011, pp. 189–200.

- [9] J. Oberg, W. Hu, A. Irturk, M. Tiwari, T. Sherwood, and R. Kastner, "Information flow isolation in I2C and USB," in *Proc. Design Automat. Conf. (DAC)* 2011, 2011, pp. 254–259.

- [10] Wishbone Specification. [Online]. Available: http://opencores.org/opencores,wishbone

- [11] Opencores.org128-Bit Verilog AES Core, Apr. 2010. [Online]. Available: http://opencores. org/project,systemcaes

- [12] J. L. Henning, "Spec cpu2006 benchmark descriptions," in *Proc. SIGARCH Comput. Archit. News*, 2006, pp. 1–17.

**Jason Oberg** is currently a PhD student in the Computer Science and Engineering Department at

the University of California, San Diego. His primary research interests are in hardware and embedded system security. He has a BS in computer engineering from the University of California, Santa Barbara in 2009.

**Timothy Sherwood** is a Professor in the Department of Computer Science at the University of California at Santa Barbara (UCSB), specializing in the development of novel computer architectures for security, monitoring, and adaptive control. Prior to joining UCSB in 2003, he has an MS and PhD from University of California at San Diego in 2003.

**Ryan Kastner** is currently a professor in the Department of Computer Science and Engineering at the University of California, San Diego. He has a PhD in computer science from the University of California, Los Angeles (UCLA) in 2002. His current research interests reside in the realm of embedded system design, in particular, the use of reconfigurable computing devices for digital signal processing and security.

■ Direct questions and comments about this article to Jason Oberg, Computer Science and Engineering, University of California, San Diego, CA 92093-0404 USA; jkoberg@cs.ucsd.edu.

62